# **RIVYERA**

reconfigure versatilely your efficient raw architecture

**ActiveRead**

Version 2.0.1.0

SciEngines GmbH Am Kiel-Kanal 2 24106 Kiel Germany

www.sciengines.com

Revision: 1.92.02 December 10, 2015

# **Table of Contents**

| 1 | Introduction                              | 4               |

|---|-------------------------------------------|-----------------|

|   | RIVYERA Implementation 2.1 FPGA Design    |                 |

| 3 | FPGA VHDL Sources 3.1 activeread_main.vhd | <b>10</b>       |

| 4 | Host C Sources 4.1 activeread.c           | 12<br>12        |

| 5 | Host Java Sources 5.1 ActiveRead.java     | <b>14</b><br>14 |

The Information in this document is provided for use with SciEngines GmbH ('SciEngines') products. No license, express or implied, to any intellectual property associated with this document or such products is granted by this document.

All products described in this document whose name is prefaced by 'COPACOBANA', 'RIVYERA', 'SciEngines' or 'SciEngines enhanced' ('SciEngines products') are owned by SciEngines GmbH (or those companies that have licensed technology to SciEngines) and are protected by patents, trade secrets, copyrights or other industrial property rights. The SciEngines products described in this document may still be in development. The final form of each product and release date thereof is at the sole and absolute discretion of SciEngines. Your purchase, license and/or use of SciEngines products shall be subject to SciEngines's then current sales terms and conditions.

Trademarks The following are trademarks of SciEngines GmbH in the United States and other countries:

- SciEngines GmbH,

- SciEngines Massively Parallel Computing,

- SciEngines Logo,

- COPACOBANA, COPACOBANA RIVYERA, RIVYERA, IPANEMA

#### Trademarks of other companies

- Intel is a registered trademark of Intel Corporation.

- Linux is a registered trademark of Linus Torvalds.

- Oracle, Oracle Enterprise Linux are a registered trademark of the Oracle Corporation.

- RedHat, RedHat Enterprise Linux are a registered trademark of the RedHat Corporation.

- Xilinx, Virtex and ISE are registered trademarks of Xilinx in the United States and other countries.

- ChipScope, CORE Generator and PlanAhead are trademarks of Xilinx, Inc.

# 1 Introduction

SciEngines RIVYERA is a high performance reconfigurable computing platform. It is capable of massive performance gains compared to standard architectures. However, it does not follow the *von Neumann* architecture and therefore it requires a different style of programming, which is illustrated in this sample. ActiveRead is a very simple communication example to get in touch with the active read mechanism which is a special mode for the <code>se\_read()</code> function. The active read is used for requesting a number of words from an FPGA, waiting for the reply and reading it. In this example, the FPGA may be asked to write an arbitrary number of words to the requester. These words initially start with 0 and are incremented word by word. It is also possible to change the starting number by writing it to an FPGA. It might be a good idea to have a look at the PingPong example first, before trying to understand this example.

# 2 RIVYERA Implementation

In contrast to the *PingPong* example, which uses the *passive read* mechanism, this example uses the *active read* mechanism.

The active read mechanism is defined by the SciEngines-API and allows the host or an FPGA to actively request and afterwards read an arbitrary number of 64 bit data words from a single FPGA. The active read is therefore internally devided into two parts:

- 1. Write a read request to an FPGA.

- 2. Wait for the answer and read it passively.

The read request is a special data packet that is sent to the target FPGA which is addressed by the active read. In contrast to regular data packet, the target command (api\_i\_tgt\_cmd) is set to CMD\_RD rather than CMD\_WR. The data itself (api\_i\_data) is then an integer number which is the number of requested data packets. It is necessary for the FPGA design to explicitly handle incoming data packets which have the target command set to CMD\_RD. Else the active read mechanism may not be used. Nevertheless, the active read is an optional feature and handling it in the FPGA design might be left away if there is no need for it.

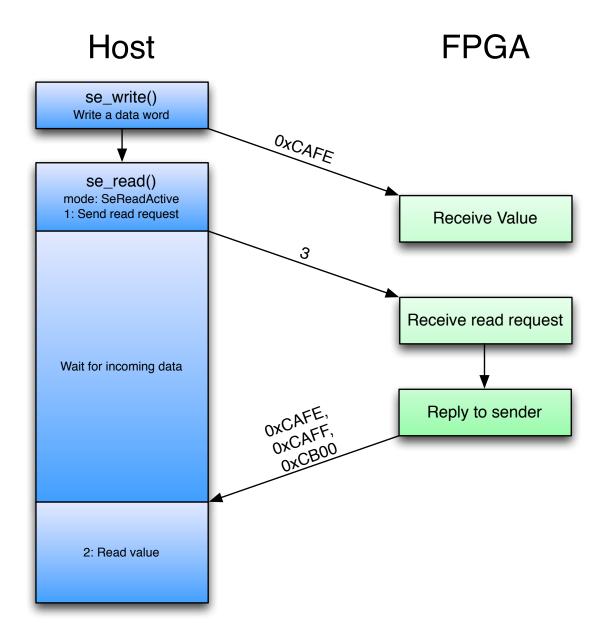

se\_read() implicitly does both parts -sending the read request and reading the requested data- when called with mode SeReadActive. But it may also be called with mode SeReadReqest to only write a read request to an FPGA. Afterwards se\_read() may be called with mode SeReadPassive to wait for the requested data and read it passively. A typical active read communication flow is illustrated in figure 1.

$\textbf{Figure 1: Communication flow:} \ \, \texttt{ar\_current\_word} \ \, \textbf{is set to} \ \, \texttt{0xCAFE} \ \, \textbf{and three data packets are read actively.}$

The ActiveRead example is intended to illustrate and help understanding the active read mechanism.

# 2.1 FPGA Design

The FPGA design's key features are (see activeread\_main.vhd in chapter 3.1):

- 1. Incoming read requests are handled for any possible target register address (0...62). The FPGA design replies to a read request by writing values to the request's source address. These written values are taken from the internal register ar\_current\_word. Each time a value is sent, it is incremented and stored again in ar\_current\_word. There are as many data packets sent as there are requested.

- 2. ar\_current\_word is not reset between different read requests.

3. ar\_current\_word may be set by sending a new value to target register address 0. Initially, ar\_current\_word is set to value 0.

Initially ar\_counter is set to 0. While there is no incoming data packet, api\_i\_empty\_in remains '1' and the if statement in line 129 is false. That means that there is no change in ar\_counter until there is an incoming read request data packet.

Lets assume there is an incoming read request (which is the active read's first part) targetting register address 0. Further lets assume the active read is about to read one data packet. The read request data packet requests one reply data packet by setting api\_i\_data\_in to 1.

#### In the first clock cycle this will happen:

The if statement in line 129 is true (api\_i\_empty\_in equals '0' and indicates an incoming data packet). Also, api\_i\_tgt\_cmd\_in is equal to CMD\_RD indicating a read request. Thus the elsif statement in line 147 is true. Then the first case in line 154 is applicable since the request's target register address is 0. Due to the request that requests one data packet, the if statement in line 155 is false (api\_i\_data\_in equals 1 but ar\_counter is still 0). So the lines 159-162 are processed (ar\_current\_word is incremented and sent; ar\_counter is incremented). Note that the read request data packet is not yet acknowledged by setting api\_i\_rd\_en\_out to '1'.

#### In the second clock cycle:

The read request is not yet acknowledged. So the first case in line 154 is still applicable. But ar\_counter now equals api\_i\_data\_in (both are 1) which means the incoming read request is now acknowledged by setting api\_i\_rd\_en to '1'. ar\_counter is reset to its default value 0.

#### Third clock cycle:

The read request is now being acknowleded. The if statement in line 129 is false due to the api\_i\_rd\_en signal being '1'. So the default assignment in line 111 resets the api\_i\_rd\_en to '0' again. In the next clock cycle the process will be ready to handle another data packet.

#### 2.2 Host Design

The host design's key features are (see activeread.c in chapter 4.1 and ActiveRead.java in chapter 5.1):

- 1. Three words are read actively from the first FPGA on the first card by using the SciEngines-host-API function se\_read() with mode SeReadActive.

- 2. Ten words are read actively from the first FPGA on the first card by using se\_read() with mode ReadRequest and again se\_read() but with mode SeReadPassive. These two function calls are identical to the se\_read() with mode SeReadActive.

- 3. ar\_current\_word is set to value <code>0xcafe</code> by writing it to the first FPGA on the first card using <code>se\_write()</code>.

- 4. Finally five words are read actively from the first FPGA on the first card.

```

\# actively reading 3 words from FPGA 0 in slot 0, register 0

src [s0 fH r0 cWR] >>> tgt [s0 f0 r0 cRD]: 0x000000000000000

tgt [s0 fH r0 cWR] <<<

src [s0 f0 r0 cRD]: 0x0000000000000000

tgt [s0 fH r0 cWR] <<<

src [s0 f0 r0 cRD]: 0x0000000000000001

src [s0 f0 r0 cRD]: 0x00000000000000002

tgt [s0 fH r0 cWR] <<<

\# requesting 10 words from FPGA 0 in slot 0, register 0

src [s0 fH r0 cWR] >>> tgt [s0 f0 r0 cRD]: 0x00000000000000

\# passively reading 10 words from FPGA 0 in slot 0, register 0

src [s0 f0 r0 cRD]: 0x00000000000000004

tgt [s0 fH r0 cWR] <<<

src [s0 f0 r0 cRD]: 0x0000000000000005

tgt [s0 fH r0 cWR] <<<

src [s0 f0 r0 cRD]: 0x0000000000000000

tgt [s0 fH r0 cWR] <<<

src [s0 f0 r0 cRD]: 0x00000000000000007

tgt [s0 fH r0 cWR] <<<

src [s0 f0 r0 cRD]: 0x00000000000000008

tgt [s0 fH r0 cWR] <<<

tgt [s0 fH r0 cWR] <<<

src [s0 f0 r0 cRD]: 0x0000000000000000

tgt [s0 fH r0 cWR] <<< src [s0 f0 r0 cRD]: 0x00000000000000b

\mbox{\#} writing the word Oxcafe to FPGA 0 in slot 0, register 0

# (for the ActiveRead example, this sets the start word for replies)

src [s0 fH r0 cWR] >>> tgt [s0 f0 r0 cWR]: 0x0000000000000cafe

\# actively reading 5 words from FPGA 0 in slot 0, register 0

src [s0 fH r0 cWR] >>> tgt [s0 f0 r0 cRD]: 0x000000000000005

tgt [s0 fH r0 cWR] <<< src [s0 f0 r0 cRD]: 0x00000000000000cafe

tgt [s0 fH r0 cWR] <<< src [s0 f0 r0 cRD]: 0x00000000000000caff

```

Figure 2: This is a communication log for the example execution. Within the squared brackets the s stands for slot, f for fpga, r for register, c for command, WR for CMD\_WR, RD for CMD\_RD and h for host.

The communication that occurs when executing this example is represented in detail in figure 2. Note that in this very simple example the FPGA and Slot addresses are hardcoded. The SciEngineshost-API functions  $se_getSlotCount()$  and  $se_getFPGACount()$  might be useful for setting addresses dynamically.

#### 3 FPGA VHDL Sources

## 3.1 activeread\_main.vhd

```

-- Project: ActiveRead

-- File: activeread_main.vhd

-- Date: Thu Nov 22 16:03:58 CET 2012

-- Author: Daniel Siebert (SciEngines GmbH)

67

-- This is the ActiveRead example project.

10

-- Copyright (c) 2012-2015, SciEngines GmbH

-- All rights reserved.

13

-- Redistribution in source or binary forms, with or without modification,

-- is not permitted without specific prior written permission.

15

-- THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

-- "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

-- LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

16

18

-- LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

-- A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

-- OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

-- SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

-- LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

-- DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

-- THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

-- (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

-- OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

19

20

21

22

23

24

25

26

27

28

librarv ieee;

use work.sciengines_api_types.all;

30

31

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

33

34

entity activeread_main is

generic (

36

37

NUM_LEDS

port (

39

40

----- APT PORTS -----

42

43

-- USER PORTS

api_clk_in

: in

std logic;

44

api_rst_in

: in

std_logic;

: out

45

api_led_out

seBusFlag_type(NUM_LEDS-1 downto 0) := (others => '0');

46

api_hw_rev_in

-- ADDRESS PORTS

: in

seHwRev_type;

47

48

api_self_contr_in

: in

seFlag_type;

49

api_next_contr_in

api_prev_contr_in

seSlotAddr_type;

seSlotAddr_type;

: in

50

: in

51

52

53

54

55

: in

api_self_slot_in

seSlotAddr_type;

api_self_fpga_in :

-- OUTPUT REGISTER PORTS

: in

seFpgaAddr_type;

api_o_clk_out

: out

std_logic;

api_o_rfd_in

: in

seFlag type;

56

57

58

59

60

api_o_tgt_slot_out

: out

seSlotAddr_type := (others => '0');

seFpgaAddr_type := (others => '0');

seRegAddr_type := (others => '0');

api_o_tgt_fpga_out

api_o_tgt_reg_out

: out

: out

seCmd_type

api_o_tgt_cmd_out

: out

:= CMD_WR;

:= (others => '0');

api_o_src_reg_out

: out

seRegAddr_type

:= CMD_WR;

seCmd_type

api o src cmd out

: out

:= (others => '0');

:= '0';

62

api_o_data_out

seData_type

63

api_o_wr_en_out :

-- INPUT REGISTER PORTS

: out

seFlag_type

64

65

: out

api_i_clk_out

std_logic;

api_i_src_slot_in

api_i_src_fpga_in

66

: in

seSlotAddr_type;

67

seFpgaAddr_type;

: in

68

api_i_src_reg_in

: in

seRegAddr_type;

69

api_i_src_cmd_in api_i_tgt_reg_in

: in

seCmd_type;

70

71

72

73

74

75

76

77

seRegAddr_type;

: in

api_i_tgt_cmd_in

: in

seCmd_type;

api_i_data_in

: in

seData_type;

seFlag_type;

api_i_empty_in

: in

api_i_am_empty_in

seFlag_type;

: out

seFlag_type

api_i_rd_en_out

end entity activeread_main;

architecture activeread_main_behave of activeread_main is

```

```

-- Define some local signals because

82

-- we can not read from the out-ports.

83

:= '0';

signal api_i_rd_en : seFlag_type

:= '0';

signal api_o_wr_en

: seFlag_type

85

signal ar_current_word : seData_type

:= (others => '0');

86

:= (others => '0');

signal ar_counter

: seData_type

88

89

90

91

-- When defining an own clock domain to

-- run the user design with a different

-- clock, the following two lines should

92

92

93

94

-- probably be altered

api_i_clk_out <= api_clk_in;

api_o_clk_out <= api_clk_in;</pre>

95

96

97

\ensuremath{\text{--}} route the internal signals to the out-ports

98

api_i_rd_en_out <= api_i_rd_en;

api_o_wr_en_out <= api_o_wr_en;</pre>

99

100

101

\mbox{--} A Spartan 6 FPGA has two LEDs for debugging purposes. \mbox{--} Set these LEDs disabled here. Comment following

102

-- line and use this signal anywhere you want to! api_led_out <= (others => '0');

103

104

105

106

activeread_process : process

107

begin

108

wait until rising_edge(api_clk_in);

109

-- Do not read anything by default.

api_i_rd_en <= '0';</pre>

110

111

112

-- Do not write anything by default.

api_o_wr_en <= '0';</pre>

113

114

115

116

-- Set the answer's target slot-,

117

-- fpga- and register-addresses.

api_o_tgt_slot_out <= api_i_src_slot_in;

api_o_tgt_fpga_out <= api_i_src_fpga_in;

api_o_tgt_reg_out <= api_i_src_reg_in;

api_o_tgt_cmd_out <= api_i_src_cmd_in;

api_o_src_reg_out <= api_i_tgt_reg_in;

api_o_src_cmd_out <= api_i_tgt_cmd_in;

118

119

120

121

122

123

124

125

if (api_rst_in = '1') then

126

127

128

-- While user_rst_in is high, the api

-- is not ready for use.

else

129

130

131

if (api_i_empty_in = '0'

and api_i_rd_en = '0') then

-- There is a new incoming data packet

132

133

134

-- and this data packet has not been read last clock cycle.

if (api_i_tgt_cmd_in = CMD_WR) then

-- this is an incoming regular data packet

-- which has been written using se_write

135

136

case api_i_tgt_reg_in is

when "000000" =>

137

138

-- this means, we set the incoming payload as start value ar_current_word <= api_i_data_in; api_i_rd_en <= '1';

139

140

141

142

api_i_rd_en

when others =>

-- only handle register 0,

-- discard incoming data packet

api_i_rd_en <= '1';

143

144

145

146

147

end case;

end case;

elsif (api_i_tgt_cmd_in = CMD_RD

and api_o_rfd_in = '1') then

-- this is an incoming read request data packet

-- that has been written using se_read with mode

-- SeReadActive or mode SeReadRequest.

-- also the API is ready for data (rfd) to be written.

148

149

150

151

152

153

154

155

156

157

case api_i_tgt_reg_in is

when "000000" =>

if (ar_counter = api_i_data_in) then

<= (others => '0');

<= '1';</pre>

ar_counter

api_i_rd_en

158

159

ar_current_word <= ar_current_word + 1;</pre>

160

161

162

ar counter

<= ar_counter + 1;

end if;

164

165

when others =>

-- only handle register 0,

-- discard any other incoming data packet

```

## 4 Host C Sources

#### 4.1 activeread.c

```

* Project: ActiveRead

File:

activeread.c

4

5

Thu Nov 22 16:25:08 CET 2012

* Author: Daniel Siebert (SciEngines GmbH)

6

7

Description:

8

* This is the ActiveRead example project.

10

11

12

* Copyright (c) 2012-2015, SciEngines GmbH

* All rights reserved.

13

14

\star Redistribution in source or binary forms, with or without modification,

* is not permitted without specific prior written permission.

15

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

* "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

* LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

16

17

A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

19

2ŏ

21

22

23

24

25

THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

26

27

28

29

30

31

32

33

34

35

#include <stdio.h>

#include <stdlib.h>

#include <unistd.h>

#include <string.h>

#include <getopt.h>

#include <SeHostAPI.h>

36

extern const char *__progname;

static const char *PROGRAM_NAME = "activeread";

static const char *PROGRAM_VERSION = "1.92.02";

static const char *COPYRIGHT_TXT = "Copyright_(c)_2012-2015,_SciEngines_GmbH";

38

41

const char* BIT_FILE = "../../fpga/vhdl/xc6slx150-3fgg676/activeread_top.bit";

const char* SIM_FILE = "../../fpga/vhdl/xc6slx150-3fgg676/activeread.sim";

43

44

45

static void printUsage() {

printf("Usage:_%s_[-options]_[BIT_FILE]\n", __progname);

printf("___\n");

printf("where_options_include:\n");

46

47

48

49

50

printf("____h_-help____print_this_help_and_exit\n");

printf("____v-h_-version____print_product_version_and_exit\n");

printf("___-m_-machine_____run_your_program_on_a_specific_machine\n");

51

52

53

54

55

56

static void printVersion() {

printf("%s_version_%s\n", PROGRAM_NAME, PROGRAM_VERSION);

printf("%s\n", COPYRIGHT_TXT);

57

58

59

static int run_program(se_machine_t machine, const char* bit_file) {

retval = EXIT_SUCCESS;

addr; /* addre

60

SE_STATUS

SE ADDR

/* address structure */

```

```

pReceive[10]; /* received data words */

send; /* send data word */

__uint64_t

63

64

_uint64_t

SE_CONTROLLERINFO controllerInfo;

size_t

tc;

66

67

printf("Running_ActiveRead_with_SciEngines_RIVYERA_Host-API_v_%02u.%02u.%02u.%02u.(%s)...\n\n",

SE_API_VERSION_MAJOR, SE_API_VERSION_MINOR, SE_API_VERSION_SP, SE_API_VERSION_REVISION);

69

70

71

72

73

74

75

76

77

78

81

82

if (machine >= se_getMachineCount()) {

printf("Error:_No_such_index:_%u\n", machine);

return EXIT_FAILURE;

printf("Allocating_machine_%u:_", machine);

API_ERROR_CHECK(se_allocMachine(machine, NULL))

/\star set address to all slots, all FPGAs. \star/

addr.contr = 0;

addr.slot = SE_ADDR_SLOT_ALL;

83

84

addr.fpga = SE_ADDR_FPGA_ALL;

addr.reg = 0;

addr.reg

85

86

87

printf("Getting_controller_information_for_machine_%u:_", machine);

API_ERROR_CHECK(se_getControllerInfo(machine, addr.contr, &controllerInfo));

printf("Programming_fpgas:_");

88

89

90

if (strcmp(controllerInfo.driver_name, "isim") == 0)

API_ERROR_CHECK(se_program(machine, &addr, SIM_FILE, 5000))

} else if (bit_file) {

91

92

93

94

API_ERROR_CHECK(se_program(machine, &addr, bit_file, 5000))

else {

API_ERROR_CHECK(se_program(machine, &addr, BIT_FILE, 5000))

95

96

97

addr.slot = 0;

addr.fpga = 0;

printf("\nActi

98

printf("\nActively_reading_3_words_from_[machine_%u,_contr_%u,_slot_%u,_fpga_%u,_reg_%u]:_",

machine, addr.contr, addr.slot, addr.fpga, addr.reg);

API_ERROR_CHECK(se_read(machine, &addr, pReceive, 3, SeReadActive, &tc, 5000))

100

printf("Received_value_at_index_%-2zu:_0x%016lx.\n", i, pReceive[i]);

101

102

103

104

printf("\nRequesting_10_words_from_[machine_%u,_contr_%u,_slot_%u,_fpga_%u,_reg_%u]:_", machine,

addr.contr, addr.slot, addr.fpga, addr.reg);

API_ERROR_CHECK(se_read(machine, &addr, NULL, 10, SeReadRequest, &tc, 5000))

printf("Passively_reading_3_words_from_[machine_%u,_contr_%u,_slot_%u,_fpga_%u,_reg_%u]:_",

machine, addr.contr, addr.slot, addr.fpga, addr.reg);

API_ERROR_CHECK(se_read(machine, &addr, pReceive, 10, SeReadPassive, &tc, 5000))

105

106

107

108

109

for (i = 0; i < tc; i++) {

printf("Received_value_at_index_%-2zu:_0x%016lx.\n", i, pReceive[i]);

110

111

112

send = 0xcafe;

114

115

API_ERROR_CHECK(se_write(machine, &addr, &send, 1, NULL, 5000))

116

117

printf("Actively_reading_5_words_from_[machine_%u,_contr_%u,_slot_%u,_fpga_%u,_reg_%u]:_", machine

, addr.contr, addr.slot, addr.fpga, addr.reg);

API_ERROR_CHECK(se_read(machine, &addr, pReceive, 5, SeReadActive, &tc, 5000))

118

119

for (i = 0; i < tc; i++) {

120

printf("Received_value_at_index_%-2zu:_0x%016lx.\n", i, pReceive[i]);

121

122

123

printf("Deprogramming_fpgas:_");

addr.slot = SE_ADDR_SLOT_ALL;

addr.fpga = SE_ADDR_FPGA_ALL;

124

125

126

API_ERROR_CHECK(se_deprogram(machine, &addr))

127

printf("Freeing_machine_%u:_", machine);

API_ERROR_CHECK(se_freeMachine(machine))

128

130

131

return retval;

133

int main(int argc, char* const argv[] ) {

/* getopt_long stores the option index here. */

134

135

136

option_index = 0;

137

char

const char

*bit_file = NULL;

se_machine_t machine = 0;

139

140

141

static struct option long_options[] = {

no_argument,

no_argument,

NULL, 'h'},

NULL, 'v'},

142

143

{"help",

{"version",

```

```

144

{"machine",

required_argument, NULL, 'm' },

145

146

"timestamp",

no_argument,

NULL, 1},

\{0, 0, 0, 0\}

147

148

149

while ((c = getopt_long(argc, argv, "hvm:", long_options, &option_index)) != -1) {

150

151

152

switch (c) {

case 'h':

printUsage();

exit(EXIT_SUCCESS);

153

154

155

break;

case 'v':

156

157

158

printVersion();

exit (EXIT_SUCCESS);

break;

159

160

161

case 'm':

se 'm':

if (sscanf(optarg, "%u", &machine) != 1) {

fprintf(stderr, "Could_not_read_argument_%s\n", optarg);

162

163

164

else(

165

break;

166

167

case 1:

printf("%s_%s\n", __DATE__, __TIME__);

168

exit(EXIT_SUCCESS);

169

170

break:

default:

171

172

173

exit(EXIT_FAILURE);

break:

174

175

if (optind + 1 < argc) {

fprintf(stderr, "Unexpected_argument:_\"%s\"\n", argv[optind + 1]);

exit(EXIT_FAILURE);</pre>

176

177

178

179

} else {

180

181

if (optind < argc) {</pre>

bit_file = argv[optind];

183

184

exit(run_program(machine, bit_file));

185

186

return 0;

```

### 5 Host Java Sources

# 5.1 ActiveRead.java

```

import com.sciengines.rivyera.api.types.*;

import com.sciengines.rivyera.api.types.exceptions.*;

import static com.sciengines.rivyera.api.SciEngines_API.*;

import static com.sciengines.rivyera.api.SciEngines_API_Const.*;

import java.nio.ByteBuffer;

ĕ

7

import java.nio.ByteOrder;

8

9

10

* Project: ActiveRead

Thu Nov 22 16:25:08 CET 2012

11

12

* @author Daniel Siebert (SciEngines GmbH)

13

14

\star This is the ActiveRead example project.

15

16

17

Copyright (c) 2012-2015, SciEngines GmbH

* All rights reserved.

18

19

* Redistribution in source or binary forms, with or without modification,

20

21

22

is not permitted without specific prior written permission.

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

23

24

25

A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

26

27

28

DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

```

```

* OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

33

34

public class ActiveRead {

35

36

37

private static final String PROGRAM_NAME = "activeread";

private static final String PROGRAM_VERSION = "1.92.02";

private static final String COPYRIGHT_TXT = "Copyright_(c)_2012-2015,_SciEngines_GmbH";

38

39

private static final String BIT_FILE = "../../../fpga/vhdl/xc6s1x150-3fgg676/activeread_top.bit";

private static final String SIM_FILE = "../../../fpga/vhdl/xc6s1x150-3fgg676/activeread.sim";

40

41

42

43

private static void printUsage() {

ivate static void printUsage() {

System.out.println("Usage:_java_" + PROGRAM_NAME + "_[-options]_[BIT_FILE]");

System.out.println("___");

System.out.println("where_options_include:");

System.out.println("___-h_--help_____print_this_help_and_exit");

System.out.println("___-v_--version_____print_product_version_and_exit");

System.out.println("___-m_--machine____print_product_version_and_exit");

}

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

60

61

62

63

64

static void printVersion() {

System.out.println(PROGRAM_NAME + "_version_" + PROGRAM_VERSION);

System.out.println(COPYRIGHT_TXT);

SeOptions

options;

SeAddress

addr;

/* address structure */

receive;

/* received data word */

long

long

send;

/* send data word

ByteBuffer payload;

SeControllerInfo controllerInfo;

tc;

65

long

66

67

options = new SeOptions(

68

SeOptions.SeWriteBehavior.se_write_async,

69

SeOptions.SeRoutingMethod.se_routing_normal);

payload = ByteBuffer.allocateDirect(8 * 10)

70

71

72

.order(ByteOrder.nativeOrder());

System.out.printf("Running_ActiveRead_with_SciEngines_RIVYERA_Host-API_v_%02d.%02d.%02d_(%s) ...\n\n", SE_API_VERSION_MAJOR, SE_API_VERSION_MINOR, SE_API_VERSION_SP, SE_API_VERSION_REVISION)

73

74

75

76

77

78

79

if (machine >= se_getMachineCount()) {

System.out.println("no_such_index:_" + machine);

System.exit(1);

80

81

try {

/ {

System.out.print("Allocating_machine_" + machine + ":_");

se_allocMachine(machine, options);

82

83

System.out.println("SUCCESS!");

85

addr = new SeAddress(0, SE_ADDR_SLOT_ALL, SE_ADDR_FPGA_ALL, 0);

System.out.printf("Getting_controller_information_for_machine_%d:_", machine);

86

controllerInfo = se_getControllerInfo(machine, addr.contr);

System.out.println("SUCCESS!");

88

89

90

System.out.print("Programming_fpgas:_");

if ("isim".equals(controllerInfo.getDriverName())) {

91

92

se_program(machine, addr, SIM_FILE, 5000);

93

} else if (bitFile != null) {

94

95

se_program(machine, addr, bitFile, 5000);

} else {

96

97

98

se program (machine, addr, BIT FILE, 5000);

System.out.println("SUCCESS!");

addr.slot = 0;

addr.fpga = 0;

100

101

102

addr.reg = 0;

103

104

System.out.printf("\nActively_reading_3_words_from_[machine_%d,_contr_%d,_slot_%d,_fpga_%d,_

reg_%d]:_",

machine, addr.contr, addr.slot, addr.fpga, addr.reg);

tc = se_read(machine, addr, payload, 3, SE_READ_ACTIVE,

105

106

107

1000);

System.out.println("Success!");

for (int i = 0; i < tc; i++) {

receive = payload.getLong(i * 8);

System.out.printf("Received_value_at_index_%-2d:_0x*016x.\n", i, receive);

}</pre>

108

109

110

112

113

114

System.out.printf("\nRequesting_10_words_from_[machine_%d,_contr_%d,_slot_%d,_fpga_%d,_reg_%d]:_",

```

```

115

machine, addr.contr, addr.slot, addr.fpga, addr.reg);

tc = se_read(machine, addr, payload, 10, SE_READ_REQUEST,

116

117

1000);

118

System.out.println("Success!");

119

120

121

122

123

1000):

124

System.out.println("Success!");

125

126

127

for (int i = 0; i < tc; i++)</pre>

receive = payload.getLong(i * 8);

System.out.printf("Received value at index %-2d: 0x%016x.\n", i, receive);

128

129

130

send = 0xcafe;

System.out.printf("\nWriting_value_0x%016x_to_[machine_%d,_contr_%d,_slot_%d,_fpga_%d,_reg_%d]:_",

131

132

send, machine, addr.contr, addr.slot, addr.fpga, addr.reg);

133

payload.putLong(0, send);

se_write(machine, addr, payload, 1, 1000);

134

135

System.out.println("Success!");

136

137

138

139

140

141

142

System.out.println("Success!");

for (int i = 0; i < tc; i++) {

receive = payload.getLong(i * 8);</pre>

143

144

145

System.out.printf("Received_value_at_index_%-2d:_0x%016x.\n", i, receive);

146

147

148

System.out.print("Deprogramming_fpgas:_");

addr.slot = SE_ADDR_SLOT_ALL;

addr.fpga = SE_ADDR_FPGA_ALL;

149

150

151

152

se_deprogram(machine, addr);

System.out.println("SUCCESS!");

153

154

System.out.print("Freeing_machine_" + machine + ":_");

se_freeMachine(machine);

System.out.println("SUCCESS!");

155

} catch(SeApiException e) {

System.err.println("Failed:_" + e.getMessage());

156

157

158

159

160

return retval;

161

}

162

163

public static void main(String[] args) {

String bitFile = null;

int machine = 0;

164

165

166

167

for (int optind = 0; optind < args.length; optind++) {

if (args[optind].equals("-h") || args[optind].equals("--help")) {</pre>

168

169

printUsage();

170

System.exit(0);

171

172

173

} else if (args[optind].equals("-v") || args[optind].equals("--version")) {

printVersion();

System.exit(0);

174

} else if (args[optind].equals("-m") || args[optind].equals("--machine")) {

175

optind++;

176

177

if (optind < args.length)</pre>

machine = Integer.parseInt(args[optind]);

178

} else {

179

System.err.println("Missing_argument_for_option_" + args[optind - 1]);

180

System.exit(1);

181

182

} else if (bitFile == null) {

183

bitFile = args[optind];

184

} else {

185

System.err.println("Unexpected_argument_\"" + args[optind] + "\"");

186

System.exit(1);

187

188

189

System.exit(run_program(machine, bitFile));

190

191

192

```

#### Thank you for choosing an original SciEngines product.

**Imprint**

Responsible for content:

Firm SciEngines GmbH

Street Am Kiel-Kanal 2

**ZIP** D-24106

City Kiel

**Country** Germany

Phone +49 431 9086200 0

Email info@sciengines.com

WWW http://www.sciengines.com

**CEO** Gerd Pfeiffer

Commercial Register Amtsgericht Kiel

Commercial Register No. HR B 9565 KI

**VAT- Identification Number** DE 814955925

Disclaimer: Any information contained in this document is confidential, and only intended for reception and use by the specified person who bought the SciEngines product. Drawings, pictures, illustration and estimations are non binding and for illustration purposes only. If you are not the intended recipient, please return the document to the sender and delete any copies afterwards. In this case any copying, forwarding, printing, disclosure and use is strictly prohibited.